Details:

Customer

Aristotle University of Thessaloniki

Technology Used

Synopsys Raphael (TCAD suite)

The Institute:

The Aristotle University of Thessaloniki is the largest university in Northern Greece.

The project:

By stacking multiple dies and connecting them with Through-Silicon Vias (TSVs), engineers can achieve higher device density, improved performance, and reduced interconnect delays.

However, this vertical integration introduces new reliability challenges. TSVs, as the backbone of 3D interconnects, are particularly susceptible to defects such as cracks and open faults (Fig. 1)—issues that can severely impact performance or even lead to complete system failure. This makes accurate electrical modeling of TSV faults not just useful, but essential for ensuring robust design and effective testing strategies.

An IEEE paper published by Aristotle University of Thessaloniki1 helps tackle this challenge by proposing a lumped analytical electrical model specifically for cracked (open-fault) TSVs. The goal is clear: to provide a fast, reliable, and physically meaningful way to represent faulty TSV behavior, enabling more effective fault detection and improved test methodologies.

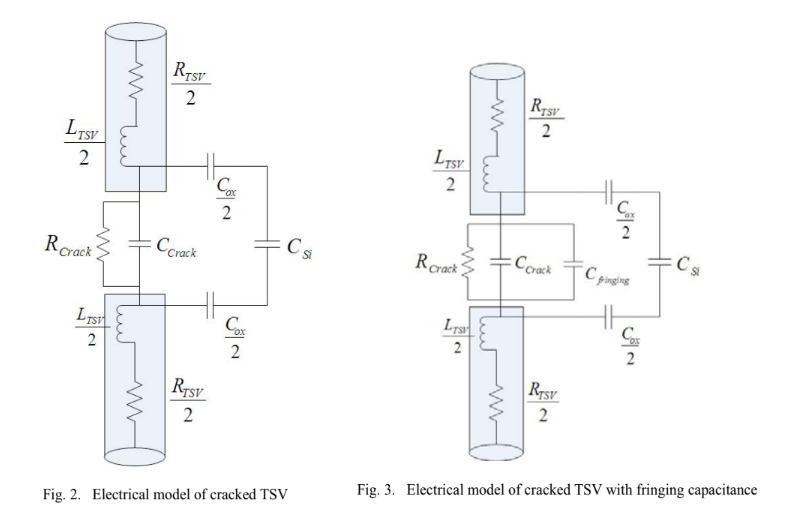

In addition to the core fault model, the authors explore two variations of capacitance modeling: one that neglects fringing capacitance and a more advanced version that incorporates it. These models (illustrated in Figure 2-3) offer different levels of fidelity, allowing designers to balance simplicity and accuracy depending on the application.

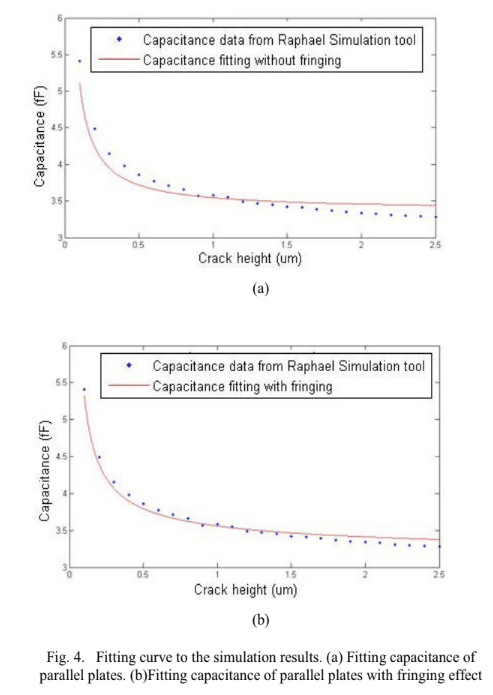

To validate the proposed approach, the analytical models are benchmarked against simulation results obtained by Synopsys Raphael, a commercial tool for extracting resistance, capacitance, and inductance. The comparisons (Figure 4) show strong agreement between the analytical predictions and Synopsys Raphael simulation data. Importantly, the version that includes fringing capacitance demonstrates even higher accuracy.

Accurate TSV fault models enable more reliable detection of defects such as cracks and open circuits—critical capabilities for manufacturing test and long-term reliability. As 3D IC adoption accelerates, these modeling approaches become key enablers for maintaining quality, reducing yield loss, and ensuring system robustness.

1Vasileios Gerakis, Christina Avdikou, Alexandros Liolios, Alkis Hatzopoulos,”Modeling and analysis of Through Silicon Via (TSV) Interconnections”, IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), p.p. 310-313, 2014.